# PalArch's Journal of Archaeology of Egypt / Egyptology

## REVIEW OF EMERGING TRENDS IN LOW POWER MULTIPLER

Sheetal Nagar<sup>1</sup>, Seema Nayak<sup>2</sup>, Govind Singh Patel<sup>3</sup>

<sup>1</sup>Ph.D Scholar SEEE LPU Phagwara and Faculty ECE IIMT College of Engineering,Greater Noida

<sup>2,3</sup> Department of ECE, IIMT College of Engineering, Greater Noida

Sheetal Nagar, Seema Nayak,Govind Singh Patel: Review Of Emerging Trends In Low Power Multipler -- Palarch's Journal Of Archaeology Of Egypt/Egyptology 17(9). ISSN 1567-214x

Keywords: Low Power Design, Wallace, Dadda, Speed, Area.

## ABSTRACT

A significant amount of power is consumed by multipliers which in turn results in lowers processing speeds. In this paper we review and investigate the use of low power multiplier to resolve the issues of various applications such as Artificial Intelligence, Machine learning, IOT(Internet of thing), FIR, IIR, DSP and Image processing, multimedia/signal Processing, patter recognition or Image Shrinking and data mining and analysis. Various Schemes and different architectures of low power Multiplier are Analyzed or Compared for betterment of the parameters like Area, Speed, Energy, Power and Delay. Various Tools used for the simulations like Mat lab, Xilinx and Verilog.

## 1. Introduction

In today era low power consumption on a integrated circuit has been high for accurate calculations and power issues[1]. Inexact (Approximate) computing is highly recommended to solve the power issues and error tolerant issues [2]. Portable devices and minimization of size always demand of the market which attract the researchers toward the [3] multiplication techniques. Popular applications of low power multiplier in human perception, DSP, machine learning, artificial intelligence, IOT and pattern recognition [4] Inexact (approximate) technique used for various levels like in circuit of the ICs, architecture of Microprocessors and correlations [5,6]. Polyphase filter banks are the applications of DSP [7] for decimation or interpolate ion [8] which are basic block in conversion of sampling rate [9]. Multiplication has error tolerant Applications [10].

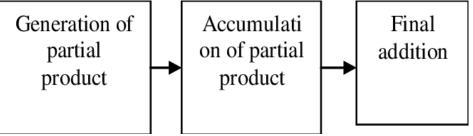

Figure 1 Conventional Wallace tree Multiplier

Basic block diagram of Conventinal Wallace tree multipler are shown in the figure 1. Wallace tree multiplier have three basic blocks for Multiplication. Which are generation of partial product, output of partial product will be served as input to the Accumulation and final block contain the Final addition.

A versatile multimedia functional unit can be design using low power parameters i.e multiplication, subtraction, addition interpolation, SAD and MAC using various configuration [11] SPST for VMFU with decrease dynamic power can be reduce with the capacitance switching minimization can be analyzed [12] and design [13] presents multiplier with dynamic range determination unit with booth codes for power saving . In Architecture design of Multiplier with SPST modification can be done with both encoder [11].

Minimization of no of full adder and half adder with reduction of tree [14] design can be used to partial product rounding consider with the deletion, truncation and reduction. To reduce the area cost truncated multiplier can be design [15-18] or fixed with multiplier [19-24].

Computation Accuracy and precision of absolute error [14] in truncated multipliers have application in the field of function Evaluation.16x16 bit single cycle 2's computers multipliers [25] use CMOS technology with fabrication on 90-nm dual Vt and frequency 1GHz with the 9mw power.

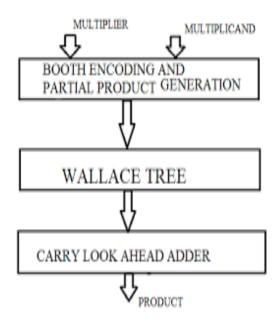

Reduction in the bit with 2's compliment in multipliers are the main component of the DSP execution cores and Accurate Embedded processor [25].Multiplication is the integral part of such application like FIR filters, IIR filters, DCTs, DSP and FFTs. These require energy efficient multiplier. To reduce the No of inputs N with the counter which convert 3iIP into 2 output in Wallace tree multipliers using log(N/2) levels of the counter [25].Figure 2 shows the Wallace booth Multiplier. In which booth algorithm and compressor are used. 3.2 compressor on first stage, 4.2 compressor on second stage and 5.2 compressor on third stage. These compressor are replaced with full adder.

#### Figure 2 Wallace Booth Multiplier.

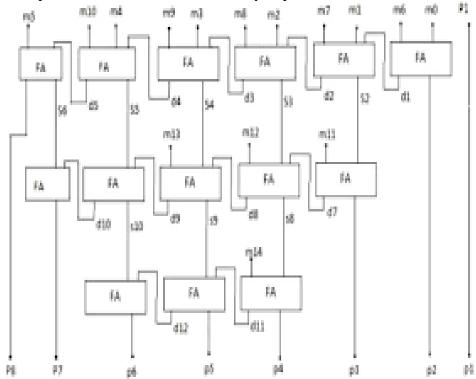

In Dadda multiplier compression of the counter member using in trees in minimized .This tree reduce no of bits and simplicity the Internal routing in the multiplier this reduction can lead Delay improvements.

#### *Figure 3.4x4 Dadda Multiplier using RCA [30]*

Dual channel multiplier [3] using 90nm CMOS technology with serialparallel schemes. Serial and parallel algorithms and the two main algorithm 7580 which are adopted to improve the performance of multiplier [3].Various types of multipliers are proposed with the booth algorithm multiplication [3] when multiplication is implemental on hardware high amount of power consumed by the process and area is highly considerable [3]Size of operand leads to the size of hardware.

Designing the approximate4-2 compressor can lead the high performance, low power consumption and power efficient circuits. Modifications in the previous design [26] leads additional accuracy. Consumption of less power, less area or less hardware requirement and error recovery module.

Practically Approximate Multiplier have application in the field of image processing , image sharpening which leads in the multimedia fields[26].Error Tolerant Application, such as Data Analysis , data mining pattern recognition, multimedia processing Approximate, logarithmic Multiplier[1].

### 2. Emerging trends:

In this section, a brief survey study is presented based on the Architecture of various multiplier and their performance parameters in MAC unit and Digital signal processing Applications.

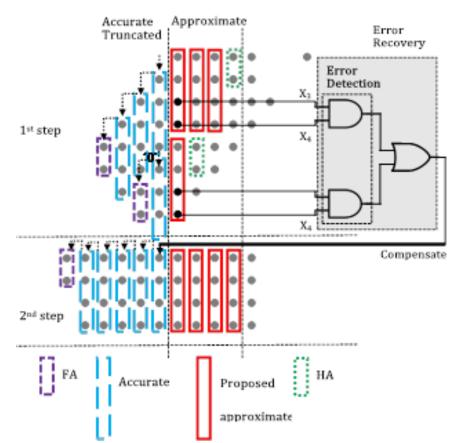

Approximate Booth multipliers are designed based on ap-proximate radix-4 modified Booth encoding (MBE) algorithms and a regular partial product array that employs an approximate Wallace tree. Two approximate Booth encoders are discussed and analyzed for error-tolerant computing. The error characteristics are analyzed with respect to the so-called approximation factor that is related to the inexact bit width of the Booth multipliers [10]. Approximate Multiplier 4-2 Compressor design modified with Carry recovery module. It is highly accurate, consumes less power and require less

hardware[26].

*Figure 3* Partial product accumulation process using truncation and proposed approximate compressors for an 8-bit approximate multiplier with error detection module and error recovery module.[26]

In this Approxiamate Multiplier Partial Product Accumulation is categories into three steps:

1. 7 bit accurate region. ( OR Gate is used to produce Carryto LSB at this Region)

2. 4 bit Approximate region

3. 4 bit Truncated Region

Error Deection and Error recovery is done at the MSB Portion[26]. Following Equations are propsed by auther for sum and carry.

```

C' \square X_1 \square X_2\square X_1 \square X_3 \square X_1\square X_4\square X_2 \square X_3 \square X2 \square X_4.S' \square (X_1 \square X_2)\square (X_3 \square X_4), [26]

```

#### 3. Conclusion:

Approxiamate multipliers have application Machine learning, Digital Signal Processor (DSP), Image Processing and image sharpening. Error Minimization is the main Constraint during the analysis of Approximate multiplier. Main Parameters considered to reduce the power, size and area of multiplier. Different Researchers uses various techniques and tools to for optimizazation technique for various Multipliers.

#### References

- Weiqiang Liu , Jiahua Xu, Danye Wang and Chenghua Wang, "Design and Evaluation of Approximate Logarithmic Multipliers for Low Power", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS–I: REGULAR PAPERS, .pp- 1549-8328. 2018.

- J. Han and M. Orshansky, "Approximate computing: An emerging paradigm for energy-efficient design," in *Proc. 18th IEEE Eur. Test Symp.*, pp. 1–6. May 2013.

- Dina M. Ellaithy and Magdy A. El-Moursy, "A 90-nm CMOS Low-Energy Dual-Channel Serial/Parallel Multiplier", IEEE. pp 132-135, 2019

- V. K. Chippa, S. T. Chakradhar, K. Roy, and A. Raghunathan, "Analysis and characterization of inherent application resilience for approximate computing," in *Proc. 50th Annu. Design Autom. Conf.* (*DAC*), 2013, Art. no. 113.

- S. Venkataramani, S. Chakradhar, K. Roy, and A. Raghunathan, "Approximate computing and the quest for computing efficiency," in *Proc. 52nd Annu. Design Autom. Conf. (DAC)*, 2015, Art. no. 120.

- [6] Q. Xu, T. Mytkowicz, and N. S. Kim, "Approximate computing: A survey," *IEEE Des. Test.*, vol. 33, no. 1, pp. 8–22, Feb. 2016.

- Martin Kumm, Member, Martin Hardieck, and Peter Zipf, "Optimization of Constant Matrix Multiplication with Low Power and High Throughput", IEEE TRANSACTIONS ON COMPUTERS, pp-1-10, January 2020.

- O. Gustafsson, K. Johansson, H. Johansson, and L. Wanhammar, "Implementation of Polyphase Decomposed FIR Filters for Interpolation and Decimation Using Multiple Constant Multiplication Techniques," in IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), 2006, pp. 924–927.

- O. Gustafsson and H. Johansson, "Efficient Implementation of FIR Filter Based Rational Sampling Rate Converters Using Constant Matrix Multiplication," in Asilomar Conference on Signals, Systems and Computers (ACSSC), 2006, pp. 888–891.

- Tongxin Yang Tomoaki Ukezono and Toshinori Sato, " A Low-Power High-Speed Accuracy-Controllable Approximate Multiplier Design", IEEE, pp 605-610. 2018.

- Kuan-Hung Chen, Yu-Min Chen, and Yuan-Sun Chu,"A Versatile Multimedia Functional Unit Design Using the Spurious Power Suppression Technique", IEEE, pp111-114, 2006.

- K. H. Chen, K. C. Chao, J. 1. Guo, J. S. Wang, and Y. S. Chu, "Design Exploration of A Spurious Power Suppression Technique (SPST) and Its Applications," IEEE Asian Solid-State Circuits Conf, pp. 341-344, Hsinchu, Taiwan, Nov. 1-3, 2005.

- 0. Chen, S. Wang, and Y. W. Wu, "Minimization of switching activities of partial products for designing low-power multipliers," IEEE Trans. VLSI, vol. 11, no. 3, pp. 418-433, June, 2003.

- Hou-Jen Ko and Shen-Fu Hsiao, "Design and Application of Faithfully Rounded and Truncated Multipliers With Combined Deletion, Reduction, Truncation, and Rounding", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 58, NO. 5,pp 304-308. MAY 2011

- M. J. Schulte and E. E. Swartzlander, Jr., "Truncated multiplication with correction constant," in *VLSI Signal Processing VI*. Piscataway, NJ:IEEE Press, 1993, pp. 388–396.

- E. J. King and E. E. Swartzlander, Jr., "Data-dependent truncation scheme for parallel multipliers," in *Proc. 31st Asilomar Conf. Signals, Syst. Comput.*,1997, pp. 1178–1182.

- M. J. Schulte, J. G. Hansen, and J. E. Stine, "Reduced power dissipation through truncated multiplication," in *Proc. IEEE Alessandro Volta MemorialInt. Workshop Low Power Des.*, 1999, pp. 61–69.

- J. E. Stine and O. M. Duverne, "Variations on truncated multiplication,"in *Proc. Euromicro Symp. Digit. Syst. Des.*, 2003, pp. 112–119.

- J. M. Jou, S. R. Kuang, and R. D. Chen, "Design of low-error fixed-width multipliers for DSP applications," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 46, no. 6, pp. 836–842, Jun. 1999.

- L.-D. Van and C.-C. Yang, "Generalized low-error area-efficient fixedwidth multipliers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 8, pp. 1608–1619, Aug. 2005.

- T.-B. Juang and S.-F. Hsiao, "Low-error carry-free fixed-width multipliers with low-cost compensation circuits," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 6, pp. 299–303, Jun. 2005.

- A. G.M. Strollo, N. Petra, and D. De Caro, "Dual-tree error compensation for high-performance fixed-width multipliers," *IEEE Trans. Circuits Syst.II, Exp. Briefs*, vol. 52, no. 8, pp. 501–507, Aug. 2005.

- N. Petra, D. De Caro, V. Garofalo, E. Napoli, and A. G.M. Strollo, "Truncated binary multipliers with variable correction and minimum

mean square error," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 6, pp. 1312–1325, Jun. 2010.

- J.-P. Wang, S.-R. Kuang, and S.-C. Liang, "High-accuracy fixed-width modified booth multipliers for lossy applications," in *IEEE Trans. VeryLarge Scale Integr. (VLSI) Syst.*, Jan. 2011, vol. 19, no. 1, pp. 52–60.

- Steven K. Hsu, Sanu K. Mathew *and* Mark A. Anders, "A 110 GOPS/W 16-bit Multiplier and Reconfigurable PLA Loop in 90-nm CMOS". IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 1, pp256-264. JANUARY 2006.

- Minho Ha and Sunggu Lee, "Multipliers with Approximate 4-2 Compressors and Error Recovery Modules", IEEE Embedded Systems Letters, pp 1943-0663 . 2017.

- Shaghayegh Vahdat, Mehdi Kamal, Ali Afzali-Kusha and Massoud Pedram, " A low energy truncation-based approximate multiplier", Elsevier Ltd Computers and Electrical Engineering,pp 1-17, August 2017.

- Nikhil, G. V., B. P. Vaibhav, Vishnu G. Naik, and B. S. Premananda. "Design of low power barrel shifter and vedic multiplier with koggestone adder using reversible logic gates." In 2017 International Conference on Communication and Signal Processing (ICCSP), pp. 1690-1694. IEEE, 2017.